DSP是信號處理系統(tǒng)的簡稱,在這個系統(tǒng)中,噪聲和EMI都是比較棘手的問題。那么如何避免在系統(tǒng)中出現(xiàn)噪聲和EMI問題呢?本文將通過電源隔離和鎖相環(huán)的方法來進(jìn)行介紹。感興趣的朋友快來看一看吧。

電源隔離和鎖相環(huán)

如何實(shí)現(xiàn)最佳供電是控制噪聲和輻射的最大挑戰(zhàn)。動態(tài)負(fù)載開關(guān)環(huán)境很復(fù)雜,包括的因素有:進(jìn)入和退出低功率模式;由總線競用和電容器充電所引起的很大的瞬態(tài)電流;由于退耦和布線不合理引起較大的電壓下降;振蕩器使線性調(diào)節(jié)器輸出過載。

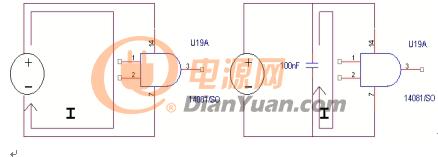

圖1:電源退耦

圖1給出了一個設(shè)計電流回路的實(shí)例,其中利用了電源線退耦。該例中的退耦電容盡可能靠近DSP。如果沒有退耦,動態(tài)電流回路將較大,這將加大電源電壓的降幅,從而產(chǎn)生電磁輻射。

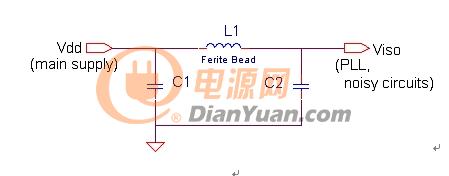

為PLL供電時,電源隔離是非常重要的,因?yàn)镻LL對噪聲非常敏感,并且對于穩(wěn)定系統(tǒng)來說,要求抖動非常低。你還需要選擇模擬的還是數(shù)字的PLL,模擬PLL對噪聲的敏感度比數(shù)字PLL要低。

圖2:PLL電源隔離

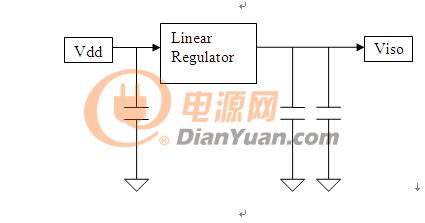

圖3:利用LDO實(shí)現(xiàn)PLL電源的隔離

如圖2所示的具有低截至頻率的∏型濾波器經(jīng)常被用來將PLL與系統(tǒng)中的其他高速電路隔離開。一個較好的辦法是利用一個低壓差(LDO)電壓調(diào)整器來獨(dú)立產(chǎn)生PLL的電源電壓,如圖5所示。該方法雖增加了成本,但確保了低噪聲和優(yōu)異的PLL性能。

聲明:本內(nèi)容為作者獨(dú)立觀點(diǎn),不代表電源網(wǎng)。本網(wǎng)站原創(chuàng)內(nèi)容,如需轉(zhuǎn)載,請注明出處;本網(wǎng)站轉(zhuǎn)載的內(nèi)容(文章、圖片、視頻)等資料版權(quán)歸原作者所有。如我們采用了您不宜公開的文章或圖片,未能及時和您確認(rèn),避免給雙方造成不必要的經(jīng)濟(jì)損失,請電郵聯(lián)系我們,以便迅速采取適當(dāng)處理措施;歡迎投稿,郵箱∶editor@netbroad.com。