在高速PCB設計中,阻抗的匹配與否關系到信號的質量優劣。阻抗匹配是指在能量傳輸時,要求負載阻抗要和傳輸線的特征阻抗相等,此時的傳輸不會產生反射,這表明所有能量都被負載吸收了。反之則在傳輸中有能量損失。下面我們一起了解下PCB設計時,何時PCB走線需要做阻抗匹配?

1 PCB走線什么時候需要做阻抗匹配?

不主要看頻率,而關鍵是看信號的邊沿陡峭程度,即信號的上升/下降時間,一般認為如果信號的上升/下降時間(按10%~90%計)小于6倍導線延時,就是高速信號,必須注意阻抗匹配的問題。導線延時一般取值為150ps/inch。

2 特征阻抗

信號沿傳輸線傳播過程當中,如果傳輸線上各處具有一致的信號傳播速度,并且單位長度上的電容也一樣,那么信號在傳播過程中總是看到完全一致的瞬間阻抗。由于在整個傳輸線上阻抗維持恒定不變,我們給出一個特定的名稱,來表示特定的傳輸線的這種特征或者是特性,稱之為該傳輸線的特征阻抗。特征阻抗是指信號沿傳輸線傳播時,信號看到的瞬間阻抗的值。特征阻抗與PCB導線所在的板層、PCB所用的材質(介電常數)、走線寬度、導線與平面的距離等因素有關,與走線長度無關。特征阻抗可以使用軟件計算。高速PCB布線中,一般把數字信號的走線阻抗設計為50歐姆,這是個大約的數字。一般規定同軸電纜基帶50歐姆,頻帶75歐姆,對絞線(差分)為100歐姆。學習PCB 找凡億教育 高質量PCB培訓

3 常見阻抗匹配的方式

1)串聯終端匹配在信號源端阻抗低于傳輸線特征阻抗的條件下,在信號的源端和傳輸線之間串接一個電阻R,使源端的輸出阻抗與傳輸線的特征阻抗相匹配,抑制從負載端反射回來的信號發生再次反射。匹配電阻選擇原則:匹配電阻值與驅動器的輸出阻抗之和等于傳輸線的特征阻抗。常見的CMOS和TTL驅動器,其輸出阻抗會隨信號的電平大小變化而變化。因此,對TTL或CMOS電路來說,不可能有十分正確的匹配電阻,只能折中考慮。鏈狀拓撲結構的信號網路不適合使用串聯終端匹配,所有的負載必須接到傳輸線的末端。串聯匹配是最常用的終端匹配方法。它的優點是功耗小,不會給驅動器帶來額外的直流負載,也不會在信號和地之間引入額外的阻抗,而且只需要一個電阻元件。常見應用:一般的CMOS、TTL電路的阻抗匹配。USB信號也采樣這種方法做阻抗匹配。

2)并聯終端匹配在信號源端阻抗很小的情況下,通過增加并聯電阻使負載端輸入阻抗與傳輸線的特征阻抗相匹配,達到消除負載端反射的目的。實現形式分為單電阻和雙電阻兩種形式。匹配電阻選擇原則:在芯片的輸入阻抗很高的情況下,對單電阻形式來說,負載端的并聯電阻值必須與傳輸線的特征阻抗相近或相等;對雙電阻形式來說,每個并聯電阻值為傳輸線特征阻抗的兩倍。并聯終端匹配優點是簡單易行,顯而易見的缺點是會帶來直流功耗:單電阻方式的直流功耗與信號的占空比緊密相關;雙電阻方式則無論信號是高電平還是低電平都有直流功耗,但電流比單電阻方式少一半。

4 常見應用:以高速信號應用較多

1)DDR、DDR2等SSTL驅動器。采用單電阻形式,并聯到VTT(一般為IOVDD的一半)。其中DDR2數據信號的并聯匹配電阻是內置在芯片中的。

2)TMDS等高速串行數據接口。采用單電阻形式,在接收設備端并聯到IOVDD,單端阻抗為50歐姆(差分對間為100歐姆)。

聲明:本內容為作者獨立觀點,不代表電源網。本網站原創內容,如需轉載,請注明出處;本網站轉載的內容(文章、圖片、視頻)等資料版權歸原作者所有。如我們采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯系我們,以便迅速采取適當處理措施;歡迎投稿,郵箱∶editor@netbroad.com。

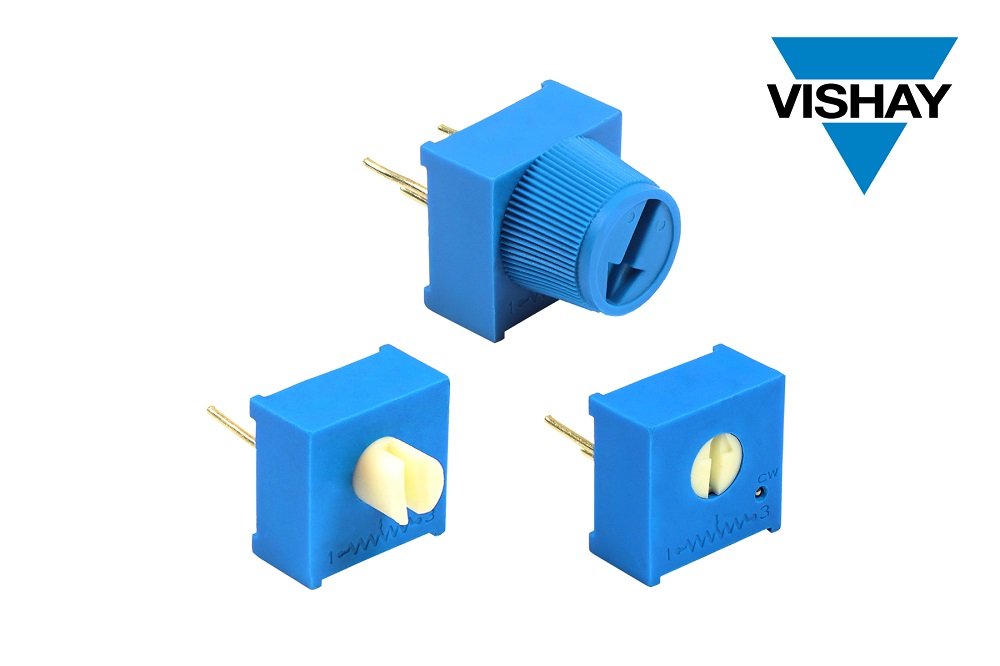

| Vishay最新工業級3/8英寸方形單匝金屬陶瓷微調器,優化PCB上的布局 | 25-07-28 15:20 |

|---|---|

| 優化簡易PCB電路板的大規模測試,提高生產效率 | 24-11-26 15:38 |

| AC-DC控制器PCB布局指南 | 24-07-10 11:12 |

| 瑞薩電子選用Altium作為統一PCB開發工具 并加速合作伙伴和客戶的解決方案設計 | 23-06-27 15:12 |

| 混合信號PCB布局設計的基本準則 | 23-04-14 11:54 |

| 微信關注 | ||

|

| 技術專題 | 更多>> | |

|

| 技術專題之EMC |

|

| 技術專題之PCB |