本文通過引入脈沖應力與電荷泵技術,解決了傳統直流方法在先進 CMOS 及高K材料可靠性評估中的三大盲區:動態恢復效應、頻率相關壽命、界面陷阱實時監測。

對于研究半導體電荷捕獲和退化行為來說,脈沖應力對典型的應力測試是一個有用的補充。NBTI(負偏置溫度不穩定性)和 TDDB(隨時間變化的介電擊穿)試驗包括應力 / 測量循環。所施加的應力電壓通常是一個直流信號,使用它是因為它更容易映射到器件模型中。然而,結合脈沖應力測試提供了額外的數據,允許更好地理解依賴頻率電路的器件性能。

傳統上,直流應力和測量技術被廣泛用于表征 CMOS 晶體管的可靠性,如由溝道熱載流子注入(HCI)和時間依賴性介電擊穿(TDDB)引起的退化。然而,隨著新的可靠性測試的發展,如金屬氧化物半導體場效應晶體管(PMOSFET)和高K材料器件中的電荷捕獲,可靠性測試的性質得到了發展。這些現象可能會對評估新過程的可靠性產生重大影響。此外,人們對評估實際運行中電路的可靠性越來越感興趣,在這些電路中多個設備是動態打開和關閉的。

新材料和結構的使用使得人們對動態可靠性測試的關注更大,在可靠性測試器件中引入脈沖或交流應力,以及在測量過程中引入脈沖來表征應力引起的界面退化。

研究發現,隨著時間的推移,電壓應力導致的界面退化或界面陷阱密度增加,是導致HCI、NBTI 等器件可靠性問題以及高K材料可靠性的關鍵因素。使用電荷泵技術在現有的直流表征測試中添加界面陷阱監測測試,對于理解這些新的可靠性問題非常有用。在本白皮書中,我們將討論一些在先進 CMOS 技術的可靠性測試中常用的電荷泵和交流應力技術。

雖然“交流壓力”一詞經常被使用,但它有點用詞不當。對于這里討論的應用,交流應力實際上是一列方形或梯形電壓脈沖。為了本文的目的,我們將使用術語“脈沖應力”,因為它并不意味著一個連續的時變的或交替的信號。

脈沖表征 - 電荷泵

電荷泵(CP)和同時進行 C-V(高頻和準靜態 C-V 的結合)測量是表征 MOS 器件中界面陷阱態密度的兩種最常用的方法。然而,隨著晶體管尺寸縮小,柵氧化物變薄,準靜態 C-V對于小于 3-4nm 的氧化物變得不現實;因此,同時 C-V 不適合新的高K材料的界面陷阱表征。

CP 是解析柵極堆疊物理的有效手段,隨著高K薄膜越來越常用于晶體管柵而變得越來越重要。CP 表征了界面和電荷捕獲現象。CP 結果的變化可用于確定典型的可靠性測試方法所引起的退化量,采用直流或脈沖應力:熱載流子注入(HCI)、負偏置溫度不穩定性(NBTI)和隨時間變化的介電擊穿(TDDB)。

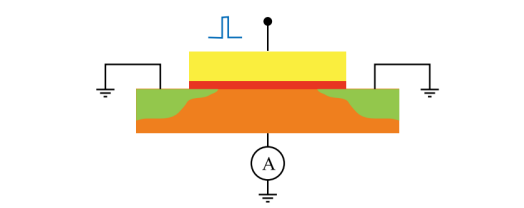

圖 1:電荷泵測量示意圖。晶體管的源極和漏極連接到地面,而柵極以固定的頻率和振幅進行脈沖

圖 1 顯示了與被測設備(DUT)的連接。基本的 CP 技術包括:對晶體管的柵極施加固定幅度、上升時間、下降時間和頻率的電壓脈沖序列時,測量基極電流。在此測試中,漏極、源連接到地面,襯底通過源測量單元(SMU)連接到地面,用于測量通過柵極的電流(Icp)。

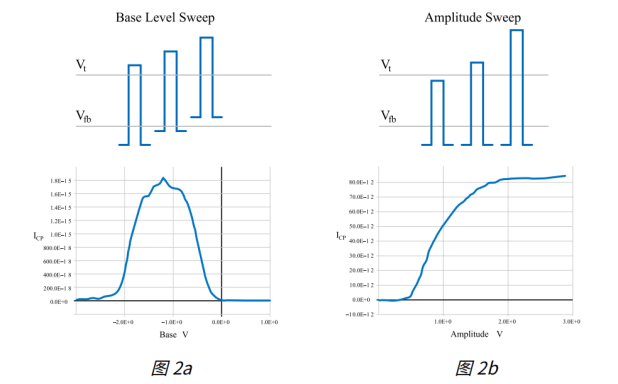

兩種最常見的 CP 技術是電壓基極掃描和幅值掃描。在電壓基極電平掃描中,周期(脈沖寬度)和電壓振幅被固定,而掃描脈沖基極電壓(圖 2a)。在每個電壓下,測量體電流并繪制基本電壓 (ICPvs Vbase),如圖 2a 所示。

圖 2 用于電荷泵送的兩種掃描類型:a)基極電壓掃描 b)脈沖幅度掃描

第二種電荷泵技術是電壓幅度掃描,它具有一個固定的基本電壓和周期 ( 脈沖頻率 ),每個掃描步驟的電壓振幅都發生了變化(圖 2b)。所獲得的數據與從電壓基極掃描中提取的數據相似,但在這種情況下,電荷泵電流與電壓幅度 (ICPvs 電壓幅度 ) 這些測量也可以在多個頻率 ( 周期 ) 上執行,以獲得界面陷阱的頻率響應。

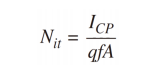

對于高K材料結構,CP 技術可以將被捕獲的電荷 (Nit) 量化為:

在硅基板 / 界面層以外的捕獲電荷可以被感知到。圖 2a 為基底電壓掃描的特征 ICP 曲線,而圖 2b 為電壓幅值掃描的特征 ICP 曲線。

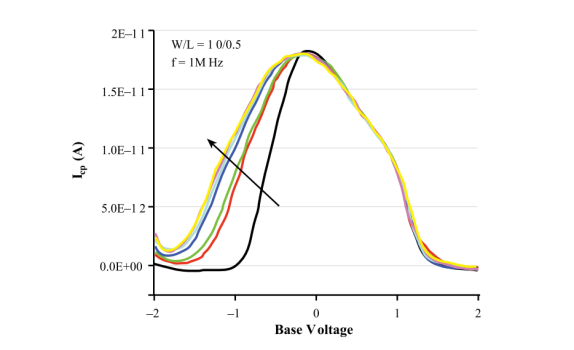

CP 技術也可用于表征界面阱形成的初始階段。圖 3 顯示了使用 1MHz 頻率的“新”CP測量(即以前未測試過的 MOSFET)。暗態電流是初始的 CP 測量值;較淺的曲線表示隨后的測量結果。請注意,在較低的電壓下,ICP曲線的形狀以及大小都發生了變化。在多次測量后,隨著效果飽和,變化趨勢就會有效地停止。曲線形狀的變化表明,CP 測量所施加的電應力導致了界面陷阱的形成。這意味著使用脈沖測量 CP 可以有效地對器件施加壓力并引起一些退化。脈沖應力下的退化是對我們理解偏置溫度不穩定性(BTI)和 TDDB 的有益補充。

圖 3. “新”器件上的電荷泵測量所引起的應力效應

BTI 和 TDDB 的脈沖應力

BTI(其中包括 NBTI 和 PBTI)和 TDDB 有相似的測試方法。這種方法包括兩個間隔、應力和測量,其中一個用高電壓施加壓力,交替定期進行測量,以確定退化量。NBTI 和TDDB 都是在高溫下進行的,以加速退化,減少測試時間,測試時間可能從一小時到兩周不等。近年來,對 PMOSFET 測試來說,NBTI 成為了一個日益重要的可靠性問題。NBTI 是一種柵極 - 通道界面的變化導致 PMOS 器件性能退化的現象。退化通常被定義為晶體管閾值電壓(VT)的增加和漏極電流(ID)的退化。在老化或場效應場景下,這種退化通過失效降低了產量。NBTI 測試有一個最近發布的行業標準。NBTI 和傳統的 HCI 測試之間最大的測試方法的區別是,在 NBTI 測試中,當應力被消除時,應力誘導的退化會出現弛豫。

這種弛豫對傳統的應力和測量技術提出了挑戰,因為當器件沒有施加電壓時,應力間隔和測量間隔之間總是有一個過渡時間。在測量間隔中,一些壓力不施加后,鑒于儀器“看到”器件性能,該技術將高估器件壽命,因為退化效應減少后,壓力將出現在測量階段。此外,使用直流應力電壓不能準確地表示器件在真實電路中所承受的應力,因為當晶體管沒有工作時,大多數器件都會經歷弛豫;因此,直流應力技術可能低估晶體管在真實電路中的壽命。隨著新技術的可靠性利潤率不斷縮小,評估晶體管的使用壽命可能是比較昂貴的。

除了弛豫作為一種動態可靠性行為,在高 κ 柵材料的晶體管中也發現了電荷捕獲。這是 因為在 CMOS 工藝中沉積高K材料的過程還不成熟,與二氧化硅門工藝相比,薄膜中還有大量的陷阱中心。當柵極被打開時,電荷可以暫時捕獲在柵極中,隨著時間的推移改變晶體管的性能,捕獲的電荷改變晶體管的閾值電壓。根據柵極的質量和捕獲條件,捕獲電荷可能需要幾十毫秒到毫秒。

高 κ 柵極內的電荷分布也會影響電場分布,從而改變高 κ 柵極的可靠性行為。同時,由于在較低的柵極電壓下去除電荷,也存在類似的弛豫效應。弛豫將導致對設備壽命的不準確估計,因為它強烈地依賴于時間,同時隨著應力測量的過渡時間,弛豫時間通常在測試環境中沒有得到很好的控制。

新的可靠性現象的動態特性要求脈沖應力來模擬電路內器件的性能。不同的電路和電路拓撲工作在不同的頻率下,因此可能需要與頻率相關的壽命提取來建立基于頻率壽命的模型。在這些應用中,脈沖應力比直流應力技術有優勢。脈沖應力對器件施加動態信號,更好地接近頻率相關的電路行為。在脈沖應力期間,應力被中斷,退化部分恢復,這恢復了器件的壽命。應力產生的界面陷阱,在應力關閉期間被部分退火或修復。由于這種恢復(或自退火)行為,可靠性工程師和科學家正在使用脈沖應力技術來更好地評估器件的壽命,因為它適用于電路內或產品內的條件。

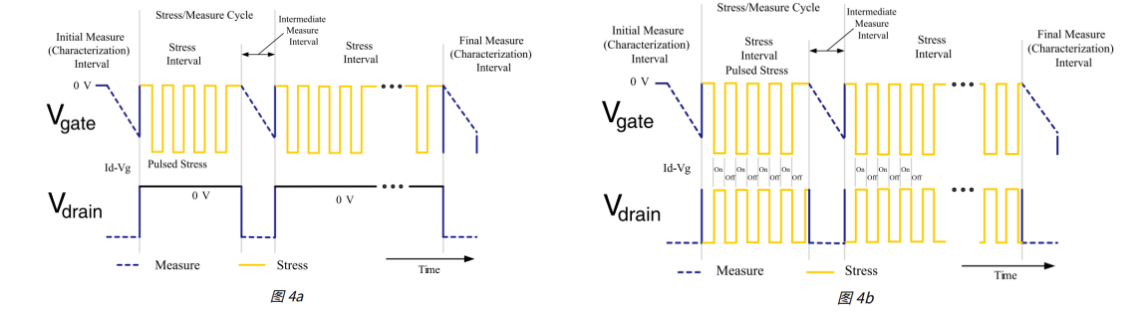

圖 4. NBTI 應力 / 測量圖,顯示了兩種不同的脈沖應力方法:a)使用傳統柵極和漏極電壓的動態;NBTI(DNBTI)b)DNBTI 模擬逆變器條件,漏極電壓與柵極電壓處于相反的相位

通過使用周期性應力來模擬器件在電路中的應力,脈沖應力基本上是一個短的直流應力,被沒有施加應力的時間中斷(圖 4)。對于 NBTI,這種應力脈沖之間的非應力部分允許退化恢復到一定程度。這種部分恢復對確定并模擬了該器件的使用壽命行為具有重要意義。部分恢復還不能被很好地理解,并且會因每個使用器件的結構、尺寸和材料的組合而有所不同。圖 4 顯示了兩個脈沖應力的例子,盡管還有其他的脈沖應力方法。圖 4a 顯示了 NBTI的脈沖應力,其中漏極電壓在應力間隔期間保持 0V。圖 4b 顯示了 NBTI 的脈沖應力,除了柵極電壓外漏極電壓是脈沖的。這第二種方法用于模擬逆變電路中的單個器件的性能。圖4b 中的柵極和漏極都受到了壓力,因此在器件退化過程中同時存在 NBTI 和 HCI。一般來說,脈沖應力技術產生更少的退化,器件的壽命更長。

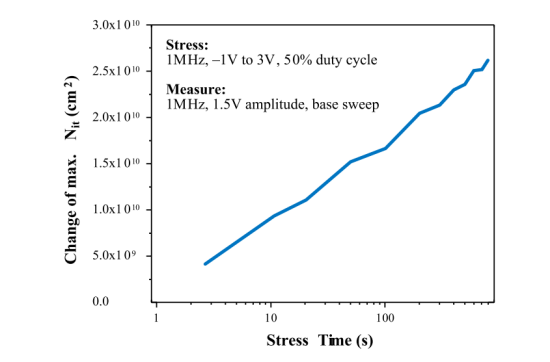

圖 5. 由于脈沖應力而導致的 Nit 退化

對于 NBTI,脈沖應力技術用于研究單個器件以及數字電路的動態行為。圖 5 顯示了不同脈沖應力持續時間導致的 Nit 的增加,結合了圖 4a 的應力方法和圖 2a 的周期性CP 測量值。

除了 BTI,TDDB 在靜態和動態故障狀態中的作用可以很好地被理解。對于在TDDB 測試期間監測 SILC(應力引發的泄漏電流),應力 / 測量圖類似于圖 4a,但 Vdrain 保 持在一個恒定的非零電壓,允許在應力期間讀取 Id。

結論

脈沖應力為研究高K薄膜的固有材料、界面和可靠性性能以及基于這些新薄膜的器件提供了關鍵的能力。脈沖應力同時測量直流電流是電荷的基礎,對測量固有電荷捕獲具有重要價值。與直流或脈沖應力結合使用,CP 還可以研究電荷捕獲,以及在高 κ-Si 界面和高K薄膜內的新電荷產生。脈沖應力還提供了一種應力方法,可以更好地模擬電路內器件所看到的實際應力,這對各種器件的可靠性測試都很有用,包括 BTI、TDDB 和 HCI。此外,脈沖應力提供了對使用直流應力不能很好監測器件可靠性行為的另一種方法。脈沖應力補充了傳統的直流技術,以提供更好地表征器件的可靠性行為。了解雙脈沖和脈沖應力測試,https://www.tek.com.cn/solutions/industry/power-semiconductor/double-pulse-testing。

關于泰克科技

泰克公司總部位于美國俄勒岡州畢佛頓市,致力提供創新、精確、操作簡便的測試、測量和監測解決方案,解決各種問題,釋放洞察力,推動創新能力。70多年來,泰克一直走在數字時代前沿。歡迎加入我們的創新之旅,敬請登錄:tek.com.cn

Tektronix是泰克公司的注冊商標。所有其他商號均為各自公司的服務標志、商標或注冊商標。

聲明:本內容為作者獨立觀點,不代表電源網。本網站原創內容,如需轉載,請注明出處;本網站轉載的內容(文章、圖片、視頻)等資料版權歸原作者所有。如我們采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯系我們,以便迅速采取適當處理措施;歡迎投稿,郵箱∶editor@netbroad.com。

| 跨域與多通道信號分析在嵌入式RF測試中的應用 | 25-08-13 13:26 |

|---|---|

| 泰克EA直流可編程電源串聯技術助力800V電動汽車高壓架構加速落地 | 25-08-04 15:09 |

| ROHM推出實現業界超低電路電流的超小尺寸CMOS運算放大器 | 25-07-29 15:02 |

| PCIe M.2接口測試的現狀、挑戰與泰克解決方案 | 25-07-03 16:56 |

| 用于高頻測量的分流電阻串聯電感補償 | 25-06-30 16:27 |

| 微信關注 | ||

|

| 技術專題 | 更多>> | |

|

| 技術專題之EMC |

|

| 技術專題之PCB |